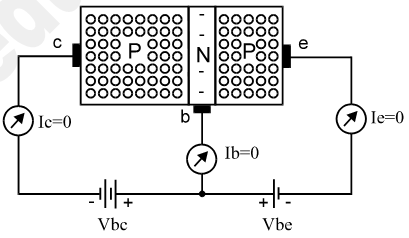

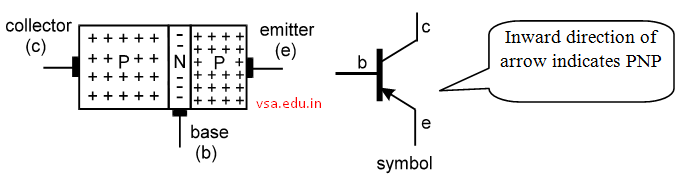

Schematic of PNP Transistor

The PNP transistor consists of three semiconductor layers: two p-type layers and one n-type layer. The n-layer is sandwiched between two p-layers. Hence it is called as P-N-P transistor. Its schematic diagram is given below.

Important Points about NPN transistor

- The area of collector layer is largest. So it can dissipate heat quickly.

- Area of base layer is smallest and it is very thin layer.

- Area of emitter layer is medium.

- Collector layer is moderately doped. So it has medium number of charges (holes).

- Base layer is lightly doped. So it has a very few number of charges (To forward bias a PNP transistor it is connected as shown in the above circuit. Read following points to understand the process easily –electrons).

- Emitter layer is heavily doped. So it has largest number of charges (holes).

- There are two junctions in this transistor – junction J1 and junction J2.

- The junction between emitter layer and base layer is called as e-b junction.

- The junction between base layer and collector layer is called as base-collector junction or b-c junction.

- The two junctions have the same potential barrier voltage of 0.6V to 0.7V, like in a diode.

Concept of Transistor Biasing

When external voltage is applied to the junction of transistor in such a direction that it cancels out the potential barrier, so that electric current flows through it, is called as transistor biasing.

Now to obtain easy current flow through the transistor it must be biased by connecting external batteries. So there must be two batteries to apply proper bias across the two junctions of the transistor.

For example, the NPN transistor can be biased using three different methods –

FF biasing: In this method both the junctions are forward biased. For this, two external batteries are connected across two junctions such that collector is negative w.r.t. base and base is positive w.r.t. emitter. This method is not useful as the transistor is in “saturation” and the current cannot be controlled easily.

RR biasing: In this method both the junctions are reverse biased. For this, two external batteries are connected across two junctions such that collector is negative w.r.t. base& base is negative w.r.t. emitter. This method is also not useful as the transistor is in “cut-off” state since current is zero.

FR biasing: This is the most common and popular method used in transistor biasing. In this method, the base-emitter junction is forward biased and collector-base junction is reverse biased.

For this, two external batteries are connected across two junctions such that collector is positive w.r.t. base and base is positive w.r.t. emitter. So by adjusting base voltage we can control total current in the transistor easily.

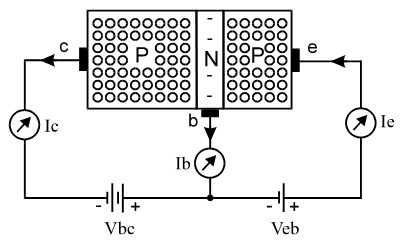

Forward Biasing of PNP Transistor

The PNP transistor can be used in two different modes: forward biased mode and the reverse biased mode. In forward biased mode, the current can easily flow through it. So it acts like a CLOSED SWITCH. However, in reverse biased mode, the current through it is practically zero and thus, it acts like an OPEN SWITCH.

To forward bias a PNP transistor it is connected as shown in the above circuit. Read following points to understand the process easily –

- The collector is connected to high negative voltage with respect to base. So b-c junction is reverse biased. Vbc >> Veb.

- The base is connected to low negative voltage with respect to emitter.

- When we increase Veb ≥ 0.7V (potential barrier voltage) the transistor is forward biased.

- Now large number of holes in emitter layer is repelled by positive terminal of Veb and they flow towards the junction.

- They cross the junction and enter into small base layer. Here some holes combine with electrons. Also some of them are attracted by negative terminal base voltage and remaining maximum number of holes flow into collector layer, crossing the base-collector junction.

- Thus, all the holes are attracted by negative terminal of Vbc.

- Thus, all the holes complete their journey back into emitter layer. So currents are produced in the transistor as shown in the above circuit.

- Thus, as per Kirchhoff Current Law, we can write: Ie = Ic + Ib

- Now when Veb is still increased, more holes are repelled by positive terminal of Veb. So emitter-base junction is more and more forward biased. Thus the base current Ib increases.

- Hence, we can say that collector current Ic is the function of base current Ib.

- So collector current is directly proportional to the base current i.e. Ic ∝ Ib.

- Maximum number of holes from emitter layer flow into collector layer. So collector current is ALMOST EQUAL to emitter current, i.e. Ic ≈ Ie.

Reverse Biasing of PNP Transistor

In this method both the junctions are reverse biased as the batteries are connected in opposite direction as shown in the adjacent diagram. Due to Vbc battery, the base-collector junction is reverse biased. Similarly, due to Vbe battery, the emitter-base junction is also reverse biased. So charges cannot flow and current in the transistor is practically zero.